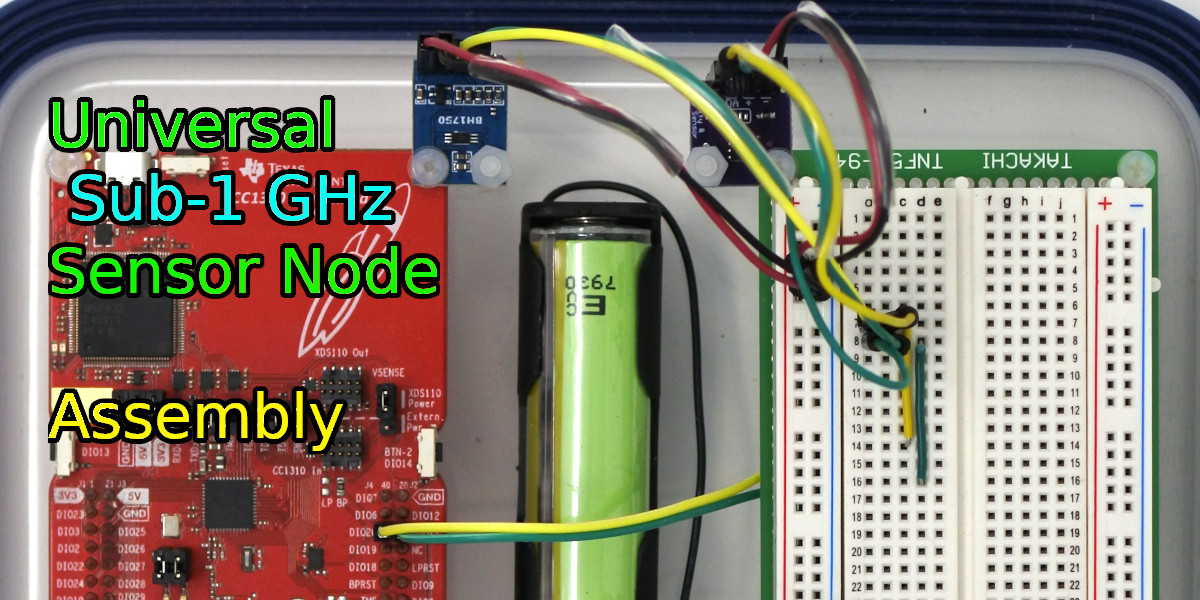

In this article I focus on the assembly of the Universal sensor node's internals, including a CC1310 LaunchPad, 18650 battery, humidity, temperature and ambient light sensors.

In this, the first article on the authentication of EdgeAI sensor nodes, using the technique of Radio Frequency Fingerprint Identification (RFFI), I recognise some of the usual suspects required to identify and authenticate wireless sensor nodes.

This article gives an overview of how I have used the rule of thirds, as a composition guideline for framing images. It explores the beauty of taking a photograph, when the rule of thirds guidelines are applied.

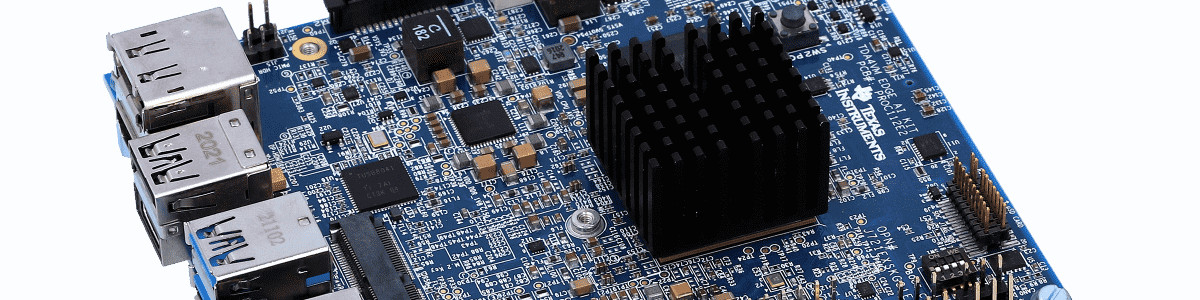

I received the TDA4VM Edge AI starter kit in the post a few days ago. The kit is supplied without a power supply, so in this quickfire post I'll present some thoughts and ideas on powering the board. Can something cheaper like a Universal USB-C power supply, typically available with the Raspberry Pi 4, be used.